# Review of Low-Cost VLSI Architecture of the Filter for Image Denoising

<sup>1</sup>Ahmad Kausar, <sup>2</sup>Prof. Rahul Shrivastava <sup>1</sup>M.Tech scholar, <sup>2</sup>Assistant Professor Department of Electronics and Communication, Sagar Institute of Science and Technology, Bhopal, India

Abstract—Image processing has many of the application in current scenario. During the image capturing or processing, some noise mix with the original image. Due to the noise issue the overall performance down or sometimes it failure. The images pixels mix with these types of the noise signal. There is various filters design which avoids or removes the noise signal. The advancement of the technology is going with the advance ICs processing. The VLSI architecture of filter design is useful in the FPGA ICs for the image processing applications. This paper reviews about the low-cost VLSI architecture of the filter for image denoising.

Keywords—Image, Denoising, VLSI, Filter, Noise, FPGA.

## I. INTRODUCTION

In many applications, picture and video signals are debased by drive commotion during obtaining or transmission. Subsequently there is a requirement for an effective and customer amicable drive commotion expulsion strategy. A Clever Region effective and low force multiplexer based Information comparator for middle filter in De-noising application is proposed. The proposed technique utilizes multiplexer based execution of acquire condition in a full subtractor which goes about as a fundamental handling component of an Information Comparator [2].

Now a-days ongoing sign handling draws in developing interests from the analysts all around the world because of its beneficial nature in tackling different deterrents that often happen in different huge sign preparing applications. In particular, advanced pictures experience the ill effects of clamor defilement and obscuring impact which presents hardships in extricating helpful data from those pictures. This requires the expulsion of clamors from those computerized pictures just as de-obscuring of such pictures continuously [4]. Commotion in the picture are arbitrary varieties in power because of characteristic or extraneous sources.

A linearized state model dependent on neighbor pixel likeness is utilized for working on the PSNR of the noisy picture. A 5-stage two equal bi-practical trapezoidal systolic cluster engineering dependent on changed Faddeev calculation (MFA) is picked as essential utilitarian square of DKF. Two equal arrangements of MFA unit are used to build the throughput by 1.6×, lessen the inertness by 1.8× while compromising an expanded usage [5]. Satellite imaging is an incredible methodology for the specialists to learn about the space data, geo-science and space data investigation. Be that as it may, during transmission satellite pictures gets ruined because of the station commotion, wrong ISO settings and so forth Satellite pictures contains tremendous measure of information which expands the size of picture, because of colossal size it requires more opportunity for transmission [6]. Presently a day's computerized signal preparing applications, for example, biometric attribute pictures, satellite imaging, clinical imaging, basically relies upon the multipliers to work on nature of picture. However, existing Logarithmic multiplier strategies produces blunder in the yield and furthermore they require more opportunity for estimation.

ISSN: 1673-064X

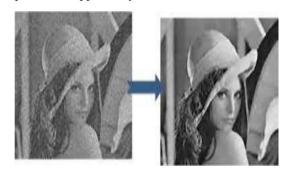

Figure 1: Leena image (a) Noisy (b) Denoised

Impulse noise brought into pictures during the time spent picture obtaining and transmission. High thickness drive clamor concealment utilizing middle sort filters result most exceedingly terrible where as these execute better to smother the low thickness motivation commotion from defiled pictures. Some condition of craftsmanship techniques can eliminate high thickness motivation clamor from adulterated pictures however some of the time the detail of pictures are changed a little and make execution time higher. In this work, propose a proficient way to deal with concealment calculation and its VLSI plan for concealment of drive commotion with higher thickness (up to almost 100%). To arrive at the point of making savvy effectively executable plan, a FPGA based reconfigurable design is proposed [8].

Pictures are regularly defiled by motivation clamor in the systems of picture securing and transmission. In this work, propose a proficient denoising plan and its VLSI engineering for the evacuation of irregular esteemed motivation clamor. To accomplish the objective of minimal expense, a low-intricacy VLSI engineering is proposed. A choice tree-based motivation commotion locator to identify the noisy pixels, and an edge-protecting filter to reproduce the power upsides of noisy pixels. Moreover, a versatile innovation is utilized to upgrade the impacts of expulsion of drive commotion [11].

Median filters ordinarily utilized in picture preparing applications for the expulsion of drive clamor. Throughout the years such countless middle filters, for example, are distinguishable middle filters, recursive middle filters, weighted middle filters, max-middle filters and multistage middle filters were created. Arranging networks are of significant worry for continuous equipment execution of filters. Arranging is a computationally costly activity as it burns-through enormous region, speed and force. In this work, successful VLSI equipment execution has been proposed as an affordable answer for arranging networks as far as region speed, power [12].

# II. LITERATURE SURVEY

C. Lien et al.,[1] C. Lien et al.,[1] presents, a minimal expense equipment engineering of the respective filter for continuous picture preparing is proposed. In view of the strategies of distance-situated gathering and equipment asset sharing, the utilization of multipliers can diminish 48% when contrasted with the past approach. Plus, a productive quantization technique is applied to lessen the size of required look into tables. The test results show that the proposed design is cost productive while keeping up with a similar picture quality, outline rate and working clock recurrence.

K. Rajini et al.,[2] The proposed work was carried out in Microwind for three distinct Models of Mosfet and various advancements. The changes in the current acquire condition of a full subtractor utilizing multiplexer just brought about decreased number of semiconductors with diminished force. For a 8 bit picture de-noising approach utilizing middle filter, which comprises of a 8 bit information comparator will require just 116 semiconductors and disperses 52.25uw of force for 90nm innovation.

ISSN: 1673-064X

M. Monajati et al.,[3] proposed rough middle filters (APMFs). They depend on the arranging organize and accomplish OK picture quality under minimal expense equipment. In this brief, foster a particular comparator to work on the abilities of those filters in clamor disposal. The design of our estimated middle filters (IMFs) is customary and particular. Additionally, present the histogram-based mistake scattering plot as another blunder assessment technique to have a superior evaluation of IMF execution. Reproduction results show that the proposed filter is viably expense in force. minimal region. Notwithstanding the tradeoff between the filtering exactness and circuit attributes, the yield nature of the filter is generally like that of the exact one. Likewise, the corruption is practically no perceptible to the natural eye.

A. Chakraborty et al.,[4] proposed a low region and profoundly exact VLSI engineering of 2D Wiener filter which can be applied for any1D/2D constant sign productively. The appropriateness of innately exceptionally exact Wiener filter chokes because of its computational intricacies. Our concentration in this article is to conquered the obstruction by lessening the computational intricacy utilizing Toeplitz framework development and its OR deterioration. have proposed a region productive multiplierless VLSI design for acknowledging 2D Wiener filter. have taken advantage of the idea of Givens turn based OR deterioration and furthermore have used the CORDIC calculation to accomplish elite of our plan. have additionally applied our proposed equipment continuously sound sign and picture denoising. The incomparability of our proposed configuration can be demonstrated from the examination of pictorial and furthermore mathematical outcomes.

B. Johnson et al.,[5] presents the limit cell of MFA is altered by supplanting the divider unit with an exceptionally pipelined two phase Query table based Newton Raphson divider. The design carried out on Xilinx Virtex-6 FPGA can denoise  $512 \times 512$  pictures continuously ( $\approx 33$  fps)

accomplishing most noteworthy throughput among the condition of craftsmanship models. A quantitative and subjective assessment of denoising on manufactured and true pictures shows the relevance of the proposed engineering.

P. Sendamarai et al.,[6]presents two-sided filtering plan and pressure decompression is done utilizing lifting based DWT. This design is carried out and mimicked utilizing XILINX ISE 14.3 test system. Decrease of the intricacy is presented by utilizing shift-add rationale plot. The proposed design works at a recurrence of 163.638MHz, when blended for Xilinx Austere III seriesfield programmable door cluster.

A. Mekkalaki et al.,[7] shows invalidate the mistake and speed up deferral of the activity of the Logarithmic Multiplier, 16×16 "Mitchell Log Multiplier" (MLM) utilizing "Karastuba Ofman Multiplier" is executed. In this undertaking Mitchell Log Multiplier with zero mistake is carried out for picture filters. The higher request 16×16, 8×8 Multipliers are planned utilizing KOM. The higher request KOM multipliers are separated into number of lower request multipliers utilizing till fundamental square of request 4×4 is gotten utilizing radix 2. 4×4 Mitchell Log Multiplier is planned with zero blunder by presenting mistake adjustment circuit. Further the 8×8 "Mitchell Log Multiplier" is tried for Gaussian filter to eliminate commotion in picture. The undertaking model is mimicked utilizing Xilinx 14.5 and integrated utilizing Simple 6 FPGA family unit. The presentation boundaries like speed, blunder region usage and PSNR are assessed. It is seen that utilizing Mitchell log multiplier zero blunder is gotten for duplication activity and PSNR of 25.11 DB and postponement of 6.629ns is acquired.

Kamarujjaman,et al.,[8] proposed engineering is working with two distinct stages - typical and restrictive arranging followed by choice based yield choice unit. In choice based yield choice stage, choice based versatile windowing idea is incorporate for better motivation commotion concealment and edge conservation. The broad outcomes for proposed engineering are shown preferred execution over any condition of-craftsmanship strategy and some as of late proposed work comprehensive amount and visual quality. The handling pace of our engineering is 254 MHz by utilizing Vertex 5 FPGA board. Low computational intricacy and no line cushion are required. Its expense is similarly low and pertinent to continuous applications, i.e clinical picture handling.

R. Pushpavalli et al.,[9] proposed keen filter is completed in two phases. In first stage the defiled picture is filtered by applying an exceptional class of exchanging middle filter. Filtered yield picture is reasonably joined with a feed forward neural organization in the subsequent stage. The interior boundaries of the feed forward neural organization are adaptively streamlined via preparing for three notable pictures. This is very successful in disposing of drive commotion. Reenactment results show that the proposed filter is unrivaled as far as wiping out drive clamor just as saving edges and fine subtleties of computerized pictures. The outcomes are contrasted and other existing filters for execution assessment.

ISSN: 1673-064X

P. Deepa et al.,[10] presents a proficient minimal expense VLSI design for the edge saving motivation commotion evacuation procedure has been proposed. The engineering contains two line cradles, register banks, motivation commotion identifier, edge situated clamor filter and drive authority. The extra room needed for the proposed equipment is two line support instead of full edge memory. Also, proposed calculation includes just fixed size window rather than variable window size. These two significantly decreases stockpiling prerequisite just as calculation intricacy. The motivation commotion indicator winds down the leftover hardware if the current pixel is sans clamor, accordingly diminishing force utilization. Further, the four phase pipeline engineering enormously works on the speed of activity. The executed edge protecting calculation brings about better visual quality for denoised picture. Hence the proposed design has less intricacy, less capacity prerequisite, low force utilization and further developed speed of activity. The engineering has been executed in Xilinx 9.2i and the outcomes are arranged for different pictures.

C. Lien, et al.,[11] proposed strategy can get better exhibitions as far as both quantitative assessment and visual quality than the past lower intricacy techniques. Additionally, the exhibition can be practically identical to the higher,- intricacy techniques. The VLSI engineering of our plan yields a handling pace of around 200 MHz by utilizing TSMC 0.18  $\mu m$  innovation. Contrasted and the cutting edge strategies, this work can diminish memory stockpiling by in excess of close to 100%. The plan requires just low computational intricacy and two line memory

cradles. Its equipment cost is low and appropriate to be applied to some constant applications.

K. Vasanth et al.,[12] proposed work utilizes another convey select comparator in the main segment which uses think about and trade capacities and its pipelined form in second segment, in this way lessening the intricacy of the arranging organizations. The proposed Convey select comparator utilizes one half subractor, 7 full subractor, not many multiplexers and inverters. The proposed calculation will defeat the issues by performing middle computation inside 7 clock cycles. This work had been contrasted and existing convey select rationale and its pipelined variant involves which possesses less region, burns-through low force and works at 113.225 MHz for the gadget Gadgets XC2s100e-7tq144.

## III. CHALLENGES

One of the fundamental challenges in the field of image processing and computer vision is image denoising, where the underlying goal is to estimate the original image by suppressing noise from a noise-contaminated version of the image. Image noise may be caused by different intrinsic (i.e., sensor) and extrinsic (i.e., environment) conditions which are often not possible to avoid in practical situations. Therefore, image denoising plays an important role in a wide range of applications such as image restoration, visual tracking, image registration, image segmentation, and image classification, where obtaining the original image content is crucial for strong performance. While many algorithms have been proposed for the purpose of image denoising, the problem of image noise suppression remains an open challenge, especially in situations where the images are acquired under poor conditions where the noise level is very high.

The purpose of noise reduction is to decrease the noise in natural images while minimizing the loss of original features and improving the signal-to-noise ratio (SNR). The major challenges for image denoising are as follows:

- Flat areas should be smooth,

- Edges should be protected without blurring,

- Textures should be preserved, and

- New artifacts should not be generated.

Since filtering is a major means of image processing, a large number of spatial filters have been applied to image denoising, which can be further classified into two types: linear filters and non-linear filters.

ISSN: 1673-064X

Spatial filters make use of low pass filtering on pixel groups with the statement that the noise occupies a higher region of the frequency spectrum. Normally, spatial filters eliminate noise to a reasonable extent but at the cost of image blurring, which in turn loses sharp edges.

The bilateral filter is a non-linear method, with this method an image can be blurred, preserving strong edges. Blurring is one of the simplest ways to smooth an image. Each pixel value from output image is a weighted sum of its neighbors in the input image.

## IV. CONCLUSION

Image denoising is the technique of removing noise or distortions from an image. There are a various range of application such as blurred images can be made clear. Therefore, image denoising plays an important role in a wide range of applications such as image restoration, visual tracking, image registration, image segmentation, and image classification, where obtaining the original image content is crucial for strong performance. This paper review about VLSI based filter techniques to denoising the image.

## REFERENCES

- C. Lien, C. Tang, P. Chen, Y. Kuo and Y. Deng, "A Low-Cost VLSI Architecture of the Bilateral Filter for Real-Time Image Denoising," in IEEE Access, vol. 8, pp. 64278-64283, 2020, doi: 10.1109/ACCESS.2020.2984688.

- 2. K. Rajini and K. Vasanth, "Area Efficient and Low Power Multiplexer based Data Comparator for Median filter in Denoising Application," 2020 International Conference on Communication and Signal Processing (ICCSP), 2020, pp. 0761-0765, doi: 10.1109/ICCSP48568.2020.9182116.

- 3. M. Monajati and E. Kabir, "A Modified Inexact Arithmetic Median Filter for Removing Salt-and-Pepper Noise From Gray-Level Images," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 4, pp. 750-754, April 2020, doi: 10.1109/TCSII.2019.2919446.

- A. Chakraborty and A. Banerjee, "A Multiplierless VLSI Architecture of QR Decomposition Based 2D Wiener Filter for 1D/2D Signal Processing With High Accuracy," 2018 4th International Conference on Computing Communication and

- Automation (ICCCA), 2018, pp. 1-6, doi: 10.1109/CCAA.2018.8777458.

- B. Johnson, N. Thomas and J. S. Rani, "An FPGA Based High throughput Discrete Kalman Filter Architecture for Real-Time Image Denoising," 2017 30th International Conference on VLSI Design and 2017 16th International Conference on Embedded Systems (VLSID), 2017, pp. 55-60, doi: 10.1109/VLSID.2017.26.

- P. Sendamarai and M. N. Giriprasad, "FPGA implementation of combined compression & denoising scheme for remote sensing images,"

2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), 2016, pp. 401-404, doi: 10.1109/RTEICT.2016.7807850.

- A. Mekkalaki and M. Kulkarni, "Design of 16\*16 high speed MLM using KOM for image filter application," 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), 2016, pp. 3504-3509, doi: 10.1109/ICEEOT.2016.7755356.

- Kamarujjaman, M. Mukherjee and M. Maitra, "An efficient FPGA based de-noising architecture for removal of high density impulse noise in images," 2015 IEEE International Conference on Research in Computational Intelligence and Communication Networks (ICRCICN), 2015, pp. 262-266, doi: 10.1109/ICRCICN.2015.7434247.

- R. Pushpavalli and G. Sivarajde, "An intelligent post processing technique for image enhancement," 2013 International Conference on Emerging Trends in VLSI, Embedded System, Nano Electronics and Telecommunication System (ICEVENT), 2013, pp. 1-5, doi: 10.1109/ICEVENT.2013.6496555.

- P. Deepa and C. Vasanthanayaki, "VLSI Implementation of Enhanced Edge Preserving Impulse Noise Removal Technique," 2013 26th International Conference on VLSI Design and 2013 12th International Conference on Embedded Systems, 2013, pp. 98-102, doi: 10.1109/VLSID.2013.170.

- C. Lien, C. Huang, P. Chen and Y. Lin, "An Efficient Denoising Architecture for Removal of Impulse Noise in Images," in IEEE Transactions on Computers, vol. 62, no. 4, pp. 631-643, April 2013, doi: 10.1109/TC.2011.256.

- 12. K. Vasanth, S. N. Raj, S. Karthik and P. P. Mol, "Fpga implementation of optimized sorting

network algorithm for median filters," INTERACT-2010, 2010, pp. 224-229, doi: 10.1109/INTERACT.2010.5706144.

ISSN: 1673-064X